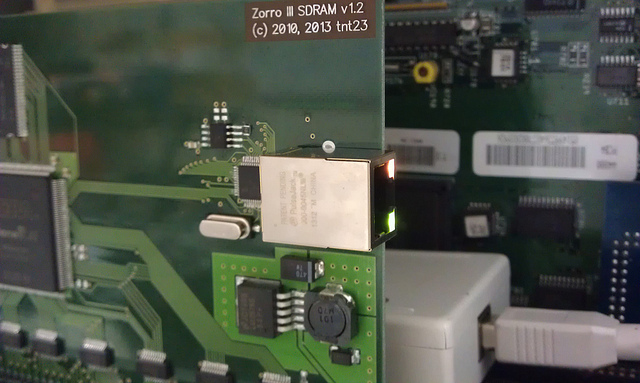

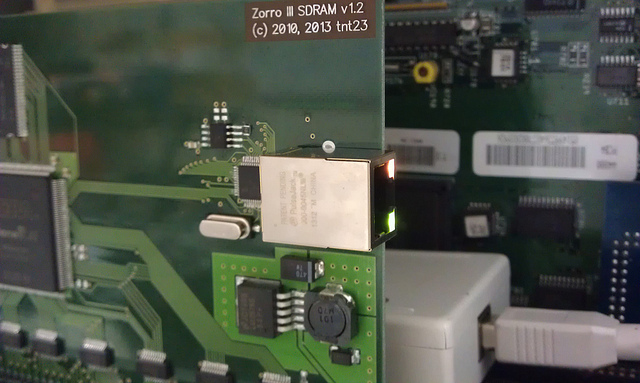

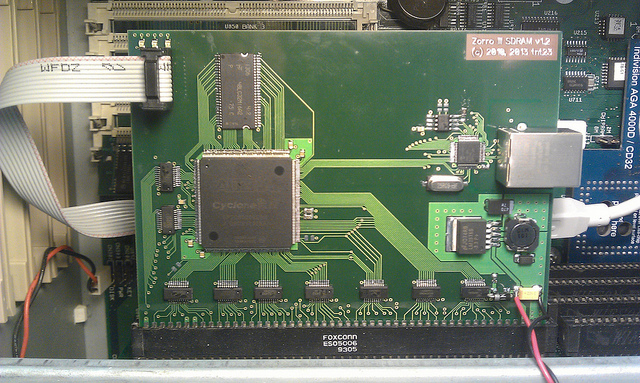

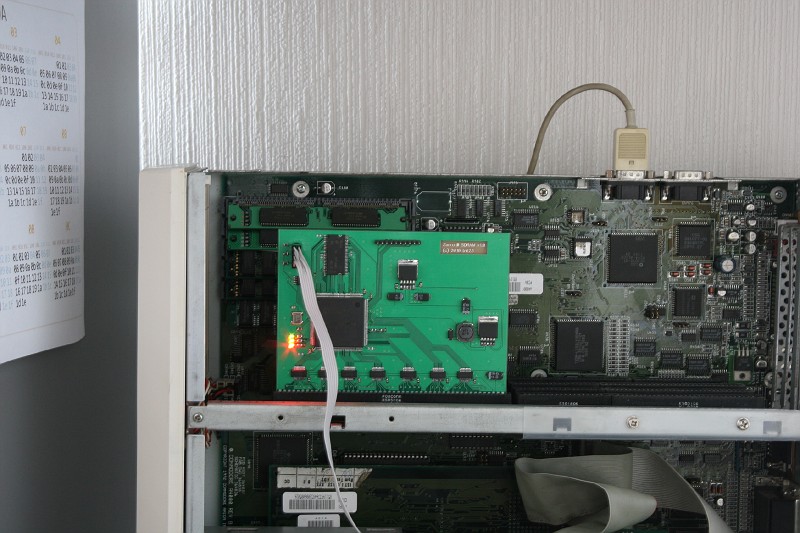

An update to original 1.0 design features 4-layer PCB, LDO-based 1.2V core voltage power supply instead of switching one, and a bunch of decoupling capacitors all over the back side of the card. Another useful addition is the 10M/100M Ethernet network adapter based on DM9000 chip from Davicom. Also the rest of Zorro bus signals are routed to FPGA, for possible support of Zorro II.

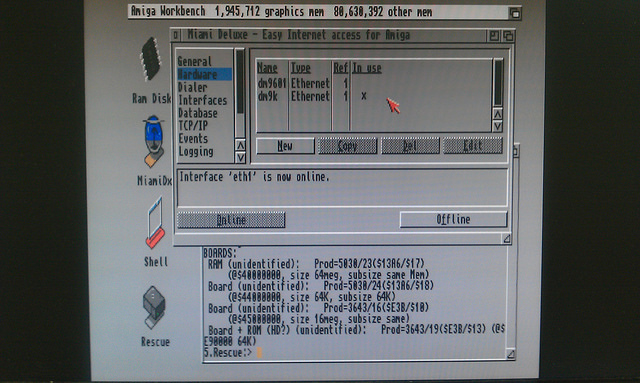

A device driver for AmigaOS 3.x has been hacked, showing RX/TX speeds of about 250-350KBytes/sec on an unexpanded A4000/030@25.

Z3SDRAM is a proof-of-concept type of project aimed at developing a memory extension for Zorro III bus using up to date technologies and components, like FPGA and synchronous DRAM.

Z3SDRAM is a proof-of-concept type of project aimed at developing a memory extension for Zorro III bus using up to date technologies and components, like FPGA and synchronous DRAM.

The project was inspired by excellent Dave Haynie's "Zorro III Bus Specification".

The Cyclone II family is not 5v tolerant, its maximum I/O working voltage of 3.3v called for some level shifters. Bidirectional IDT Quickswitches are excellent choice for this task, with their delays of 0.25ns.

Version 1.0 is a 2-layer PCB carrying 64 megabytes of SDRAM.

Project page at Google Code

© 2009, 2010, 2013, 2014 tnt23